http://dx.doi.org/10.35596/1729-7648-2025-23-5-5-11

УДК 544.653.22

## ВЕРТИКАЛЬНЫЕ ТОКОПРОВОДЯЩИЕ ПЕРЕХОДЫ В ДИЭЛЕКТРИЧЕСКИХ ПОДЛОЖКАХ НА ОСНОВЕ АНОДНОГО ОКСИДА АЛЮМИНИЯ

А. Д. ЦАЛАДОНОВ, Д. В. РЕВЕНЬКО, С. А. БИРАН, А. В. КОРОТКЕВИЧ, П. Э. НОВИКОВ, К. В. КОРСАК

Белорусский государственный университет информатики и радиоэлектроники (Минск, Республика Беларусь)

Аннотация. Развитие технологий 2,5D- и 3D-интеграций кристаллов предъявляет к корпусам изделий микроэлектроники повышенные требования. Для изготовления корпусов перспективным материалом является анодный оксид алюминия, который позволяет формировать межслойные вертикальные электрические соединения различных слоев без дополнительных операций создания отверстий в межслойной изоляции. Это дает возможность получать на поверхности последующие слои с хорошей планаризацией. В статье рассмотрен способ изготовления подложек из пористого анодного оксида алюминия с изолированными токопроводящими площадками с помощью сквозного локального анодирования алюминия. Приведена методика исследования изоляционных свойств полученных диэлектрических подложек с различными способами улучшения качества изоляции токопроводящих каналов. Представлены результаты исследования токов утечки изолированных токопроводящих каналов в зависимости от приложенного напряжения.

**Ключевые слова:** 2,5D- и 3D-интеграция кристаллов, корпуса изделий микроэлектроники, наноструктурированные материалы, пористый анодный оксид алюминия, локальное анодирование.

Конфликт интересов. Авторы заявляют об отсутствии конфликта интересов.

**Для цитирования.** Вертикальные токопроводящие переходы в диэлектрических подложках на основе анодного оксида алюминия / А. Д. Цаладонов [и др.] // Доклады БГУИР. 2025. Т. 23, № 5. С. 5–11. http://dx.doi.org/10.35596/1729-7648-2025-23-5-5-11.

# VERTICAL CONDUCTIVE TRANSITIONS IN DIELECTRIC SUBSTRATES BASED ON ANODIC ALUMINUM OXIDE

ARSENI D. TSALADONOV, DIANA V. REVENKO, SIARHEI A. BIRAN, ALEXANDR V. KOROTKEVICH, PAVEL E. NOVIKOV, KIRYL V. KORSAK

Belarusian State University of Informatics and Radioelectronics (Minsk, Republic of Belarus)

Abstract. The development of 2.5D and 3D crystal integration technologies imposes increased requirements on the housings of microelectronic products. A promising material for the manufacture of housings is anodic aluminum oxide, which allows the formation of interlayer vertical electrical connections of different layers without additional operations of creating holes in the interlayer insulation. This makes it possible to obtain subsequent layers on the surface with good planarization. The article considers a method for manufacturing substrates from porous anodic aluminum oxide with insulated conductive pads using through local anodizing of aluminum. A methodology for studying the insulating properties of the obtained dielectric substrates with various methods for improving the quality of insulation of conductive channels is presented. The results of a study of leakage currents of isolated conductive channels depending on the applied voltage are presented.

**Keywords:** 2.5D and 3D crystal integration, microelectronics product housings, nanostructured materials, porous anodic aluminum oxide, local anodization.

**Conflict of interests.** The authors declare no conflict of interests.

**For citation.** Tsaladonov A. D., Revenko D. V., Biran S. A., Korotkevich A. V., Novikov P. E., Korsak K. V. (2025) Vertical Conductive Transitions in Dielectric Substrates Based on Anodic Aluminum Oxide. *Doklady BGUIR*. 23 (5), 5–11. http://dx.doi.org/10.35596/1729-7648-2025-23-5-5-11 (in Russian).

#### Введение

По прогнозам зарубежных аналитических компаний, прирост капитализации рынка корпусирования изделий микроэлектроники составляет 9 % ежегодно и к 2030 г. достигнет 60 млрд долл. США [1, 2]. В настоящее время в связи с появлением и развитием технологий 2,5D- и 3D-интеграций кристаллов к корпусам интегральных микросхем предъявляются повышенные требования, в частности, к механическим и изоляционным свойствам [3].

Анодный оксид алюминия благодаря своим электрофизическим параметрам является перспективным материалом для применения в качестве основы корпусов изделий микроэлектроники. Использование наноструктурированных диэлектрических подложек на основе пористого анодного оксида алюминия позволяет формировать межслойные вертикальные электрические соединения различных слоев без дополнительных операций создания отверстий в межслойной изоляции [4, 5]. Это дает возможность формировать на поверхности последующие слои с хорошей планаризацией. Для оптимизации процессов проектирования и моделирования электрических характеристик корпусированных устройств необходимы данные изоляционных свойств материалов, из которых изготавливается корпус.

## Методика проведения эксперимента

В качестве образцов для исследования диэлектрических свойств подложек с вертикальными токопроводящими переходами на основе анодного оксида алюминия использовали подложки с изолированными проводящими кругами различного диаметра. Для изготовления образцов брали заготовки размерами 60×48 мм из алюминиевой фольги толщиной 100 мкм. Загрязнения с поверхности подложек удаляли раствором хромового ангидрида. Чтобы сгладить микронеровности поверхности, проводили травление в растворе NaOH в течение 30 мин. Далее для снятия внутренних механических напряжений осуществляли отжиг заготовок в термошкафу при температуре 250 °C в течение часа. Перед выполнением локального анодирования на поверхности заготовок при помощи фотолитографии формировали маску из фоторезиста. Анодирование проводили в растворе лимонной кислоты в потенциостатическом режиме при напряжении 100 В для получения пленки плотного анодного оксида алюминия на открытых участках подложки. После этого фоторезистивную маску удаляли с поверхности подложки. Перед нанесением второй маски из фоторезиста выполняли пористое анодирование в растворе ортофосфорной кислоты в потенциостатическом режиме при напряжении 90 В в течение 10 мин. Сформированный слой пористого оксида позволяет улучшить адгезию фоторезиста перед последующим сквозным анодированием.

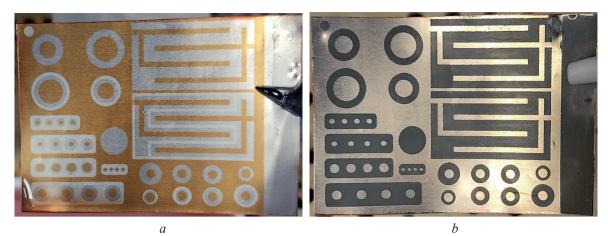

Далее на поверхности заготовок формировали маску из фоторезиста заданной конфигурации (рис. 1, a). Сквозное окисление алюминия проводили в растворе щавелевой кислоты в гальваностатическом режиме при плотности тока  $15 \text{ MA/cm}^2$ . Анодирование выполняли в специальной ванне с постоянным перемешиванием электролита и при поддержании постоянной температуры  $20 \, ^{\circ}$ С. Время анодирования составило  $8 \, ^{\circ}$ 4 до полного падения тока анодирования. Затем удаляли сформированную на поверхности подложки маску из фоторезиста (рис. 1, b).

Для исследования качества изоляции полученные образцы размещали на предметном столике микроскопа МБС-10. Токоподвод к проводящим площадкам осуществляли с помощью зондов с вольфрамовыми иглами. Измерение токов утечки проводили с помощью измерителя характеристик полупроводниковых приборов Л2-56. В режиме «Утечка» Л2-56 позволяет измерять токи порядка 1 нА. Один из зондов подключали к внешней проводящей части образцов, а второй — поочередно к токопроводящим площадкам (рис. 2). Далее измеряли токи утечки в зависимости от приложенного напряжения. Напряжение варьировалось от 200 до 1000 В с шагом 100 В.

На рис. 2 показан образец с токопроводящими каналами при различных способах изоляции: групповая изоляция, индивидуальная изоляция с варьированием ширины изолирующего кольца пористого анодного оксида алюминия, индивидуальная изоляция с использованием кольца с комбинированным плотным и пористым анодным оксидом алюминия. Параметры исследуемых площадок приведены в табл. 1.

**Рис. 1.** Образец для исследования: a, b — до и после сквозного анодирования **Fig. 1.** Sample for examination: a, b — before and after through anodizing

**Рис. 2.** Образец для исследования с пронумерованными токопроводящими площадками **Fig. 2.** Test specimen with numbered conductive pads

**Таблица 1.** Параметры исследуемых площадок **Table 1.** Parameters of the studied sites

| Номер площадки | Диаметр, мм |                        |                         |

|----------------|-------------|------------------------|-------------------------|

|                | площадки    | кольца плотного оксида | кольца пористого оксида |

| 1              | 4           | _                      | 8                       |

| 2              | 6           | _                      | 10                      |

| 3              | 6           | 8                      | 10                      |

| 4              | 4           | 6                      | 8                       |

| 5              | 1           | 2                      | _                       |

| 6              | 1           | 3                      | _                       |

| 7              | 2           | 3                      | _                       |

| 8              | 2           | 4                      | _                       |

| 9              | 0,5         | 1                      | _                       |

| 10             | 2           | _                      | 7                       |

| 11             | 2           | _                      | 5                       |

| 12             | 2           | _                      | 4                       |

| 13             | 2           | 3                      | 4                       |

| 14             | 2           | 3                      | 5                       |

| 15             | 2           | 4                      | 5                       |

| 16             | 2           | 5                      | 7                       |

## Результаты исследований и их обсуждение

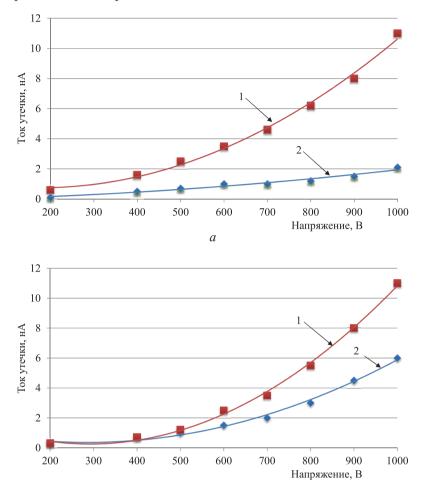

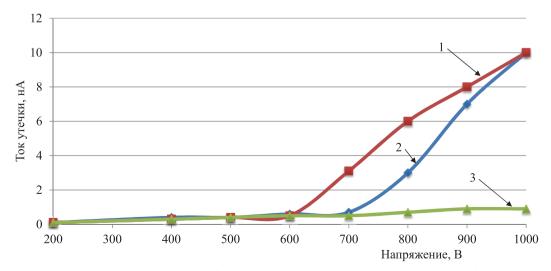

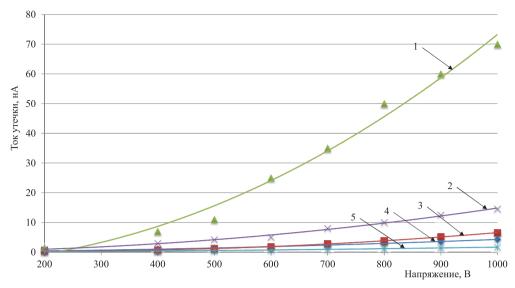

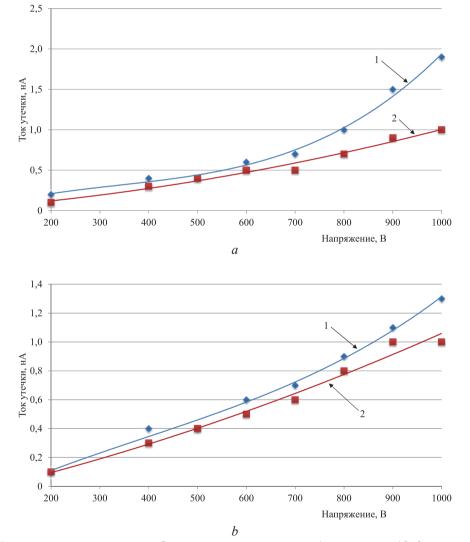

Результаты измерений токов утечки в зависимости от приложенного напряжения исследуемых площадок представлены на рис. 3–6.

**Рис. 3.** Зависимость токов утечки образцов от напряжения: a-1 – площадка 3, 2 – площадка 2; b-1 – площадка 4, 2 – площадка 1 **Fig. 3.** Dependence of leakage currents of samples on voltage: a-1 – pad 3, 2 – pad 2; b-1 – pad 4, 2 – pad 1

b

**Рис. 4.** Зависимость токов утечки образцов от напряжения на площадках: 1-14; 2-11; 3-15 **Fig. 4.** Dependence of leakage currents of samples on the voltage on the pads: 1-14; 2-11; 3-15

**Рис. 5.** Зависимость токов утечки образцов от напряжения на площадках: 1-7; 2-8; 3-6; 4-5; 5-9 **Fig. 5.** Dependence of leakage currents of samples on the voltage on the pads: 1-7; 2-8; 3-6; 4-5; 5-9

**Рис. 6.** Зависимость токов утечки образцов от напряжения: a-1 – площадка 12, 2 – площадка 13; b-1 – площадка 10, 2 – площадка 16

**Fig. 6.** Dependence of leakage currents of samples on voltage: a - 1 – pad 12, 2 – pad 13; b - 1 – pad 10, 2 – pad 16

#### Заключение

1. Показана возможность изготовления диэлектрических подложек с изолированными токопроводящими каналами с помощью локального сквозного анодирования через фоторезистивную маску.

2. Проведено исследование токов утечки образцов с различными способами изоляции токопроводящих каналов. Установлено, что у каналов с индивидуальной изоляцией токи утечки составляют единицы наноампер при напряжении 1000 В, а при использовании группового метода изоляции — десятки наноампер. Использование дополнительного кольца из плотного анодного оксида алюминия позволяет незначительно улучшить изоляционные свойства при применении индивидуальной изоляции.

## Список литературы

- Advanced Packaging Market Size, Share & Trends Analysis Report by Packaging Type (Flip-Chip, Fan-Out WLP, Embedded-Die, Fan-In WLP, 2.5D/3D), Application (Consumer Electronics, Automotive, Industrial, Healthcare), Region, with Growth Forecasts, 2025–2030 [Electronic Resource]. Mode of access: https://www.researchandmarkets.com/reports/6085858/advanced-packaging-market-size-share-and-trends. Date of access: 26.05.2025.

- 2. Advanced Packaging Market: Global Industry Analysis and Forecast (2024–2030) [Electronic Resource]. Mode of access: https://www.maximizemarketresearch.com/market-report/global-advanced-packaging-market/30807/. Date of access: 26.05.2025.

- 3. Гагарина, Л. Г. Особенности разработки метода классификации плоских QFN-корпусов для применения в составе автоматизированных систем технической подготовки производства изделий микроэлектроники / Л. Г. Гагарина, Ю. В. Рубцов // Известия вузов. Электроника. 2022. Т. 27, № 3. С. 322–332.

- 4. Hosseinabadi, Z. Developing Cu Pore-Filling Percentage in Hard Anodized Anodic Aluminum Oxide Templates with Large Diameters / Z. Hosseinabadi, A. Ramazani, M. Almasi Kash // Materials Chemistry and Physics. 2015. Vol. 260.

- 5. Nanostructured Anodic-Alumina-Based Dielectrics for High-Frequency Integral Capacitors / A. Mozalev [et al.] // Thin Solid Films. 2014. Vol. 550. P. 486–494.

Поступила 31.03.2025

Принята в печать 27.06.2025

#### References

- 1. Advanced Packaging Market Size, Share & Trends Analysis Report by Packaging Type (Flip-Chip, Fan-Out WLP, Embedded-Die, Fan-In WLP, 2.5D/3D), Application (Consumer Electronics, Automotive, Industrial, Healthcare), Region, with Growth Forecasts, 2025–2030. Available: https://www.researchandmarkets.com/reports/6085858/advanced-packaging-market-size-share-and-trends (Accessed 26 May 2025).

- 2. Advanced Packaging Market: Global Industry Analysis and Forecast (2024–2030). Available: https://www.maximizemarketresearch.com/market-report/global-advanced-packaging-market/30807/ (Accessed 26 May 2025).

- 3. Gagarina L. G., Rubtsov Y. V. (2022) Peculiarities of Development of the Method of Classification of Flat QFN-Cases for Application in the Automated Systems of Technical Preparation of Production of Microelectronics Products. *News of Universities. Electronics.* 27 (3), 322–332 (in Russian).

- 4. Hosseinabadi Z., Ramazani A., Almasi M. (2015) KashDeveloping Cu Pore-Filling Percentage in Hard Anodized Anodic Aluminum Oxide Templates with Large Diameters. *Materials Chemistry and Physics*. 260.

- 5. Mozalev A., Sakairi M., Takahashi H., Habazaki H., Hubalek J. (2014) Nanostructured Anodic-Alumina-Based Dielectrics for High-Frequency Integral Capacitors. *Thin Solid Films*. 550, 486–494.

Received: 31 March 2025 Accepted: 27 June 2025

## Вклад авторов / Authors' contribution

Авторы внесли равный вклад в написание статьи / The authors contributed equally to the writing of the article.

#### Сведения об авторах

**Цаладонов А.** Д., магистрант каф. микро- и наноэлектроники, Белорусский государственный университет информатики и радиоэлектроники (БГУИР)

**Ревенько** Д. В., магистрант каф. микро- и наноэлектроники, БГУИР

**Биран С. А.,** ст. преп. каф. микро- и наноэлектроники, БГУИР

**Короткевич А. В.,** канд. техн. наук, доц., доц. каф. микро- и наноэлектроники, БГУИР

**Новиков П. Э.,** инж.-электрон. науч.-исслед. лаб. «Компьютерное проектирование микро- и нано-электронных систем», БГУИР

**Корсак К. В.,** мл. науч. сотр. науч.-исслед. лаб. «Компьютерное проектирование микро- и наноэлектронных систем», БГУИР

#### Адрес для корреспонденции

220013, Республика Беларусь, Минск, ул. П. Бровки, 6 Белорусский государственный университет информатики и радиоэлектроники

Тел.: +375 17 293-88-90 E-mail: biran@bsuir.by Биран Сергей Андреевич

#### Information about the authors

**Tsaladonov A. D.,** Master's Student at the Microand Nanoelectronics Department, Belarusian State University of Informatics and Radioelectronics (BSUIR)

**Revenko D. V.,** Master's Student at the Micro- and Nanoelectronics Department, BSUIR

**Biran S. A.,** Senior Lecture at the Department of Micro- and Nanoelectronics, BSUIR

**Korotkevich A. V.,** Cand. Sci. (Tech.), Associate Professor, Associate Professor at the Department of Microand Nanoelectronics, BSUIR

**Novikov P. E.,** Electronics Engineer of the R&D Laboratory "CAD in Micro- and Nanoelectronics Systems", BSUIR

**Korsak K. V.,** Junior Researcher of the R&D Laboratory "CAD in Micro- and Nanoelectronics Systems", BSUIR

#### Address for correspondence

220013, Republic of Belarus, Minsk, P. Brovki St., 6 Belarusian State University of Informatics and Radioelectronics Tel.: +375 17 293-88-90

E-mail: biran@bsuir.by Biran Siarhei Andreevich