http://dx.doi.org/10.35596/1729-7648-2022-20-3-20-25

Оригинальная статья Original paper

УДК 621.382.322

# УЛУЧШЕННАЯ МОДЕЛЬ ДВУХЗАТВОРНОГО JFET ДЛЯ АНАЛОГОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Я.Д. ГАЛКИН<sup>1, 2</sup>, О.В. ДВОРНИКОВ<sup>3</sup>, В.А. ЧЕХОВСКИЙ<sup>2</sup>

<sup>1</sup>Белорусский государственный университет информатики и радиоэлектроники (г. Минск, Республика Беларусь)

<sup>2</sup>Институт ядерных проблем Белорусского государственного университета (г. Минск, Республика Беларусь)

<sup>3</sup>Минский научно-исследовательский приборостроительный институт (г. Минск, Республика Беларусь)

Поступила в редакцию 12 октября 2021

© Белорусский государственный университет информатики и радиоэлектроники, 2022

Аннотация. Двухзатворные полевые транзисторы с управляющим *p-n*-переходом часто применяются в аналоговых интегральных микросхемах для обеспечения предельно малого входного тока и емкости при управлении верхним затвором. Схемотехнический синтез и моделирование аналоговых микросхем с таким полевым транзистором возможны только при наличии моделей, адекватно описывающих особенности его работы, а именно — изменение вольт-амперных характеристик, управляя верхним затвором при подаче постоянного обратного напряжения на нижний затвор. В статье рассмотрена модернизация известной электрической модели двухзатворного полевого транзистора для программы LTSpice, заключающаяся в учете влияния напряжения на нижнем затворе путем включения в цепь верхнего затвора двух последовательно соединенных функциональных источников напряжения, один из которых обеспечивает совпадение результатов измерений и моделирования тока стока при малом напряжении между верхним затвором и истоком, а второй — при напряжении между верхним затвором и истоком, близком к напряжению отсечки. Приведена методика идентификации параметров функциональных источников напряжения. Предложенную модель двухзатворного полевого транзистора целесообразно использовать при схемотехническом проектировании различных аналоговых устройств, особенно электрометрических операционных усилителей и зарядочувствительных усилителей.

**Ключевые слова:** полевой транзистор с управляющим p-n-переходом, двухзатворный транзистор, электрическая модель, моделирование вольт-амперных характеристик.

Конфликт интересов. Авторы заявляют об отсутствии конфликта интересов.

**Для цитирования.** Галкин Я.Д., Дворников О.В., Чеховский В.А. Улучшенная модель двухзатворного JFET для аналоговых интегральных микросхем. Доклады БГУИР. 2022; 20(3): 20-25.

# DOUBLE GATE JFET IMPROVED MODEL FOR ANALOG INTEGRATED CIRCUITS

YAROSLAV D. GALKIN<sup>1, 2</sup>, OLEG V. DVORNIKOV<sup>3</sup>, VLADIMIR A. TCHEKHOVSKI<sup>2</sup>

<sup>1</sup>Belarusian State University of Informatics and Radioelectronics (Minsk, Republic of Belarus)

<sup>2</sup>Institute for Nuclear Problems of Belarusian State University (Minsk, Republic of Belarus)

<sup>3</sup>Minsk Research Instrument-Making Institute JSC (MNIPI JSC) (Minsk, Republic of Belarus)

Submitted 12 October 2021

© Belarusian State University of Informatics and Radioelectronics, 2022

Abstract. A double gate JFETs are often used in analog integrated circuits to provide an extremely low input current and capacitance when the top gate is controlled. Circuit synthesis and modeling of analog IC with such a field-effect transistor are possible only if there are models that adequately describe the features of its operation, namely, changing of the current-voltage characteristics by the top gate controlling when a constant reverse voltage is applied to the bottom gate. The article considers the modernization of the well-known electrical model of the double gate field-effect transistor for the LTSpice software, which includes taking into account the influence of the top gate voltage by connecting two series-connected functional voltage sources to the top gate, one of which ensures the coincidence of the measurement results and the simulation of the drain current at a low voltage between the top gate and the source, and the second – when the voltage between the top gate and the source is close to the cutoff voltage. A method for identifying the parameters of functional voltage sources is presented. The proposed model of a double gate field-effect transistor is advisable to use in the IC design of various analog devices, especially electrometric operational amplifiers and charge-sensitive amplifiers.

Keywords: junction field-effect transistor, double gate transistor, electric model, I-V characteristic simulation.

**Conflict of interests.** The authors declare no conflict of interests.

**For citation.** Galkin Y.D., Dvornikov O.V., Tchekhovski V.A. Double Gate JFET Improved Model for Analog Integrated Circuits. Doklady BGUIR. 2022; 20(3): 20-25.

## Введение

Двухзатворные полевые транзисторы с управляющим *p-n*-переходом (double gate junction field-effect transistor, DG JFET), формируемые на одной подложке с биполярными транзисторами (bipolar junction transistor, BJT) интегральных микросхем (ИМС), обычно имеют асимметричную структуру и обусловленные этим различные площади верхнего (top gate, TG) и нижнего (bottom gate, BG) затворов.

Меньшая площадь *p-n*-перехода и, следовательно, малая емкость и обратный ток верхнего затвора по сравнению с нижним в интегральных DG JFET используются в электрометрических операционных усилителях для обеспечения крайне малого входного тока на уровне десятков фемтоампер и большой полосы пропускания [1, 2]. Кроме того, применение паразитного ВЈТ между верхним и нижним затворами позволяет оптимизировать параметры различных зарядочувствительных усилителей [3–5].

Для обеспечения схемотехнического синтеза новых высококачественных аналоговых ИМС авторами разработана конструкция DG JFET, совместимого с типовым технологическим маршрутом изготовления комплементарных интегральных ВЈТ, изготовлены и исследованы экспериментальные образцы DG JFET, на основании результатов измерений предложена электрическая модель DG JFET для LTSpice и методика идентификации параметров [6, 7].

Созданная электрическая модель позволяет учесть особенности применения двухзатворного JFET в аналоговых микросхемах: управление соединенными затворами, управление верхним затвором с заданием постоянного напряжения на нижнем, использование

Доклады БГУИР

Т. 20, № 3 (2022)

DOKLADY BGUIR

V. 20, № 3 (2022)

паразитного биполярного транзистора между верхним и нижним затворами, однако имеется погрешность в области малых токов стока.

Целью настоящей статьи является рассмотрение модернизированной модели DG JFET, более адекватно описывающей вольт-амперные характеристики (BAX) в области малых токов стока.

## Сравнение известной и улучшенной модели двухзатворного JFET

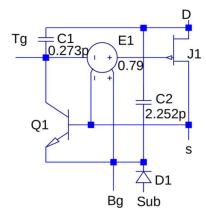

Известная эквивалентная электрическая схема DG *p*-JFET для программного обеспечения LTSpice приведена на рис. 1 [6], а на рис. 2 — предлагаемая улучшенная электрическая схема. Назначение всех элементов эквивалентной схемы и методики идентификации их параметров подробно рассмотрены в [6].

На схеме, показанной на рис. 1, применен источник напряжения, управляемый напряжением E1, коэффициент передачи GAIN которого определяется из условия

$$GAIN = \frac{V_{THTG_0}}{V_{THBG_0}},\tag{1}$$

где  $V_{T\!H\!B\!G\!_0}$  — напряжение отсечки при управлении нижним затвором и напряжении между верхним затвором и истоком  $V_{T\!G\!S} = 0$  В;  $V_{T\!H\!T\!G\!_0}$  — напряжение отсечки при управлении верхним затвором и напряжении между нижним затвором и истоком  $V_{B\!G\!S} = 0$  В.

Как указывалось, в соответствии с результатами измерений  $V_{THIG_0}$  /  $V_{THBG_0}$  = 0,68, но для лучшего совпадения результатов измерений и моделирования в широком диапазоне токов стока коэффициент передачи был выбран 0,79 [6].

**Рис. 1.** Эквивалентная электрическая схема DG p-JFET в LTSpice

**Fig. 1.** Equivalent electrical circuit DG *p*-JFET in LTSpice

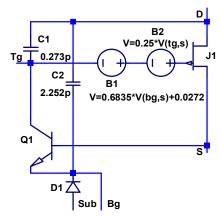

**Рис. 2.** Улучшенная эквивалентная электрическая схема DG p-JFET

**Fig. 2.** Advanced equivalent electrical circuit DG *p*-JFET

На схеме рис. 2 источник E1 заменен на последовательное соединение функциональных источников напряжения B1 и B2 [8], причем выходное напряжение первого зависит от напряжения между нижним затвором и истоком, которое в соответствии с правилами LTSpice обозначено как V(bg,s), а выходное напряжение второго — от напряжения между верхним затвором и истоком V(tg,s).

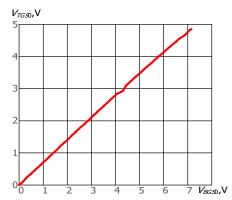

Функциональная зависимость источника В1 найдена как аппроксимация экспериментальной зависимости напряжения верхнего затвора  $V_{TGS0}$ , обеспечивающего тот же ток стока, что и напряжение нижнего затвора  $V_{BGS0}$  (рис. 3), где  $V_{TGS0} = V_{TGS}$  при  $V_{BGS} = 0$  В,  $V_{BGS0} = V_{BGS}$  при  $V_{TGS} = 0$  В. Для рис. 3 получена зависимость y = 0.6835x + 0.0272 с величиной достоверности аппроксимации  $R^2 = 0.9997$ .

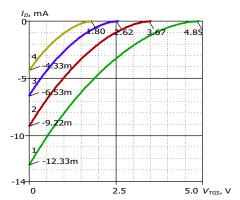

На рис. 4 приведена экспериментальная BAX DG p-JFET при управлении верхним затвором  $V_{TGS}$  и различном напряжении на нижнем  $V_{BGS}$ , причем указаны численные значения

для наиболее важных точек ВАХ, а именно: максимального тока стока  $I_{DMAX} = I_D$  при  $V_{TGS} = 0$  В и напряжения отсечки  $V_{TH} = V_{TGS}$  при  $I_D = 1$  мкА.

**Рис. 3.** Экспериментальная зависимость напряжения верхнего затвора  $V_{TGS0}$ , обеспечивающего тот же ток стока, что и напряжение нижнего затвора  $V_{BGS0}$

Fig. 3. Experimental dependence of the top gate voltage  $V_{TGS0}$ , providing the same drain current as the bottom gate voltage  $V_{BGS0}$

**Рис. 4.** Экспериментальная BAX DG *p*-JFET при управлении верхним затвором:  $1 - V_{BGS} = 0$  B,  $2 - V_{BGS} = 1$  B,  $3 - V_{BGS} = 2$  B,  $4 - V_{BGS} = 3$  B **Fig. 4.** Experimental I-V characteristic of DG p-JFET when the top gate is controlled:  $1 - V_{BGS} = 0$  V,

$2 - V_{BGS} = 1 \text{ V}, 3 - V_{BGS} = 2 \text{ V}, 4 - V_{BGS} = 3 \text{ V}$

Введение источника В1 с предложенной аппроксимацией его выходного напряжения позволяет точно подстроить значения  $I_{DMAX}$  при разном  $V_{BGS}$ , а изменением масштабирующего коэффициента источника В2 обеспечивается подстройка  $V_{TH}$  также при разном  $V_{BGS}$ .

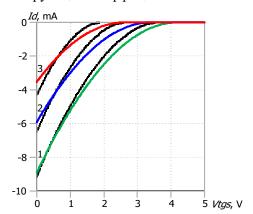

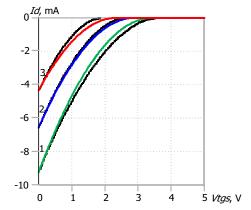

Преимущества модернизированной модели по сравнению с исходной иллюстрируют рис. 5, 6, на которых приведено сравнение результатов измерений и моделирования BAX с использованием моделей на рис. 1, 2.

Анализ результатов, приведенных на рис. 6, позволяет утверждать, что применение эквивалентной электрической схемы, показанной на рис. 2, обеспечивает удовлетворительное моделирование ВАХ двухзатворного полевого транзистора в диапазоне напряжения  $V_{BGS}$  от 1 до 3 В, что вполне достаточно для схемотехнического проектирования аналоговых схем.

Для адекватности модели в другом диапазоне напряжения  $V_{BGS}$  необходимо уточнить масштабирующий коэффициент источника B2.

**Рис. 5.** Результаты измерений (точки) и моделирования (сплошная линия) BAX DG p-JFET для модели рис. 1 при управлении верхним затвором:  $1-V_{BGS}=1$  B,  $2-V_{BGS}=2$  B,  $3-V_{BGS}=3$  B

**Fig. 5.** Results of measurements (dots) and simulations (solid line) of *I-V* characteristics DG *p*-JFET for fig. 1 model when top gate is controlled:  $1 - V_{BGS} = 1 \text{ V}$ ,  $2 - V_{BGS} = 2 \text{ V}$ ,  $3 - V_{BGS} = 3 \text{ V}$

**Рис. 6.** Результаты измерений (точки) и моделирования (сплошная линия) BAX DG p-JFET для модели рис. 2 при управлении верхним затвором:  $1-V_{BGS}=1$  B,  $2-V_{BGS}=2$  B,  $3-V_{BGS}=3$  B

**Fig. 6.** Results of measurements (dots) and simulations (solid line) of *I-V* characteristics DG *p*-JFET for fig. 2 model when top gate is controlled:  $1 - V_{BGS} = 1 \text{ V}$ ,  $2 - V_{BGS} = 2 \text{ V}$ ,  $3 - V_{BGS} = 3 \text{ V}$

Доклады БГУИР

Т. 20, № 3 (2022)

DOKLADY BGUIR

V. 20, № 3 (2022)

#### Заключение

Для схемотехнического проектирования предложена электрическая модель двухзатворного JFET, учитывающая особенности его включения в аналоговых микросхемах: управление соединенными затворами, управление верхним затвором с заданием постоянного напряжения на нижнем, использование паразитного биполярного транзистора между верхним и нижним затворами.

Повышение адекватности описания вольт-амперных характеристик двухзатворного JFET при управлении верхним затвором и при подаче постоянного обратного напряжения на нижний затвор достигнуто за счет включения в цепь верхнего затвора двух последовательно соединенных функциональных источников напряжения, один из которых обеспечивает совпадение результатов измерений и моделирования тока стока при малом напряжении между верхним затвором и истоком, а второй — при напряжении между верхним затвором и истоком, близком к напряжению отсечки.

Предложенную модель рекомендуется использовать при схемотехническом проектировании различных аналоговых микросхем, особенно электрометрических операционных усилителей и зарядочувствительных усилителей с входным двухзатворным JFET.

## Список литературы

- 1. Close J.P., Counts L.W. A 50-fA junction-isolated operational amplifier. *IEEE Journal of Solid State Circuits*. 1988;23(3):843-851. DOI: 10.1109/4.328.

- 2. Nanver L.K., Goudena E.J.G. Design considerations for integrated high-frequency p-channel JFETs. *IEEE Transactions on Electron Devices*. 1988;35(11):1924-1934. DOI: 10.1109/16.7406.

- 3. Fazzi A., Rehak P. «Gate-to-gate» BJT obtained from the double-gate input JFET to reset charge preamplifiers. *Nuclear Instruments and Methods in Physics Research*. 1996;A377:453-458. DOI: 10.1016/0168-9002(96)00238-0.

- 4. Fazzi A., Rehak P. A double-gate double-feedback JFET charge-sensitive preamplifier. *Nuclear Instruments and Methods in Physics Research*. 1996; A380(1-2):346-349. DOI: 10.1016/S0168-9002(96)00355-5.

- 5. Baturitsky M.A., Dvornikov O.V. The double-gate p-JFET-inputted amplifier for low-capacitance detectors. *Nuclear Instruments and Methods in Physics Research*. 1998;419(1):99-104. DOI: 10.1016/S0168-9002(98)00900-0.

- 6. Галкин Я.Д., Дворников О.В., Чеховский В.А., Прокопенко Н.Н. Экспериментальные исследования и модель двухзатворного JFET для аналоговых интегральных микросхем. Доклады БГУИР. 2021;19(7):5-12. DOI: 10.35596/1729-7648-2021-19-7-5-12.

- 7. Дворников О.В., Чеховский В.А., Прокопенко Н.Н., Галкин Я.Д., Кунц А.В., Чумаков В.Е. Проектирование аналоговых микросхем для экстремальных условий эксплуатации на основе базового матричного кристалла МН2ХА031. *Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС)*. 2021;1(2):37-46. DOI:10.31114/2078-7707-2021-2-37-46.

- 8. Володин В.Я. *LTspice: компьютерное моделирование электронных схем.* Санкт-Петербург: БХВ-Петербург; 2010.

### References

- 1. Close J.P., Counts L.W.A 50-fA junction-isolated operational amplifier. *IEEE Journal of Solid State Circuits*. 1988;23(3):843-851. DOI: 10.1109/4.328.

- 2. Nanver L.K., Goudena E. J. G. Design considerations for integrated high-frequency p-channel JFETs. *IEEE Transactions on Electron Devices*. 1988;35(11):1924-1934. DOI: 10.1109/16.7406.

- 3. Fazzi A., Rehak P. «Gate-to-gate» BJT obtained from the double-gate input JFET to reset charge preamplifiers. *Nuclear Instruments and Methods in Physics Research*. 1996;A377:453-458. DOI: https://doi.org/10.1016/0168-9002(96)00238-0.

- 4. Fazzi A., Rehak P. A double-gate double-feedback JFET charge-sensitive preamplifier. *Nuclear Instruments and Methods in Physics Research.* 1996; A380(1-2):346-349. DOI: 10.1016/S0168-9002(96)00355-5.

- 5. Baturitsky M.A., Dvornikov O.V. The double-gate p-JFET-inputted amplifier for low-capacitance detectors. *Nuclear Instruments and Methods in Physics Research*. 1998;419(1):99-104. DOI: 10.1016/S0168-9002(98)00900-0.

6. Galkin Y.D., Dvornikov O.V., Tchekhovski V.A., Prokopenko N.N. [Experimental studies and a double gate JFET model for analog integrated circuits]. *Doklady BGUIR = Doklady BGUIR*. 2021;19(7):5-12. DOI: 10.35596/1729-7648-2021-19-7-5-12. (In Russ.)

- 7. Dvornikov O.V., Tchekhovsky V.A., Prokopenko N.N., Galkin Y.D., Kunts A.V., Chumakov V.E. [Analog integrated circuits design for extreme environmental conditions on the base of master slice array MH2XA031]. *Problemyrazrabotki perspektivnyh mikro- i nanoelektronnyh sistem (MES)*. 2021;1(2):37-46. DOI:10.31114/2078-7707-2021-2-37-46. (In Russ.)

- 8. Volodin V.Y. [LTspice: computer modeling electonic systems]. S.-Peterburg.: BHV-Peterburg; 2010. (In Russ.)

## Вклад авторов

Галкин Я.Д. разработал модель двухзатворного транзистора, выполнил измерения ВАХ двухзатворных транзисторов и анализ полученных результатов.

Дворников О.В. выполнил анализ современного состояния проблемы по теме работы, сформулировал цель и задачи исследований, провел идентификацию параметров моделей.

Чеховский В.А. участвовал в разработке методик и измерениях параметров двухзатворных транзисторов.

### **Authors' contribution**

Galkin Y.D. has designed the DG JFET model, carried out I-V measurements of DG JFET and analysis of obtained results.

Dvornikov O.V. has analyzed the current state of the problem, formulated the goals and objectives of the work and performed the identification of model parameters.

Tchekhovski V.A. has taken part in the design of methods and parameters measurements DG JFET.

### Сведения об авторах

Галкин Я.Д., аспирант Белорусского государственного университета информатики и радиоэлектроники, младший научный сотрудник лаборатории электронных методов и средств эксперимента НИУ «Институт ядерных проблем» Белорусского государственного университета.

Дворников О.В., д.т.н., доцент, главный научный сотрудник ОАО «Минский научно-исследовательский приборостроительный институт».

Чеховский В.А., заведующий лабораторией «Электронные методы и средства эксперимента» НИУ «Институт ядерных проблем» Белорусского государственного университета.

#### Адрес для корреспонденции

220013, Республика Беларусь, г. Минск, ул. П. Бровки, 6, Белорусский государственный университет информатики и радиоэлектроники; тел. +375-257-250-775 e-mail: galkinyaroslav@gmail.com Галкин Ярослав Денисович

#### Information about the authors

Galkin Y.D., Postgraduate at the Belarusian State University of Informatics and Radioelectronics, Junior Researcher at the Electronic Methods and Experiment Means Laboratory of Research Institute for Nuclear Problems of Belarusian State University.

Dvornikov O.V., Dr. of Sci., Associate Professor, Main Researcher at the Minsk Research Instrument-Making Institute JSC.

Tchekhovski V.A., Head of the "Electronic Methods and Experiment Means Laboratory" of the Research Institute for Nuclear Problems of Belarusian State University.

#### Address for correspondence

220013, Republic of Belarus, Minsk, P. Brovki St., 6, Belarusian State University of Informatics and Radioelectronics; tel. +375-257-250-775 e-mail: galkinyaroslav@gmail.com Galkin Yaroslav Denisovich